# Broadband Circuits for Optical Fiber Communication

EDUARD SÄCKINGER

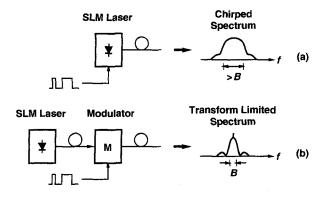

Broadband Circuits for Optical Fiber Communication This Page Intentionally Left Blank

## Broadband Circuits for Optical Fiber Communication

**Eduard Säckinger**

A JOHN WILEY & SONS, INC., PUBLICATION

Copyright © 2005 by John Wiley & Sons, Inc. All rights reserved.

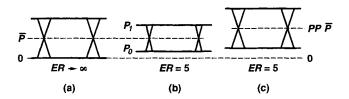

Published by John Wiley & Sons, Inc., Hoboken, New Jersey. Published simultaneously in Canada.

No part of this publication may be reproduced, stored in a retrieval system or transmitted in any form or by any means, electronic, mechanical, photocopying, recording, scanning or otherwise, except as permitted under Section 107 or 108 of the 1976 United States Copyright Act, without either the prior written permission of the Publisher, or authorization through payment of the appropriate per-copy fee to the Copyright Clearance Center, Inc., 222 Rosewood Drive, Danvers, MA 01923, (978) 750-8400, fax (978) 646-8600, or on the web at www.copyright.com. Requests to the Publisher for permission should be addressed to the Permissions Department, John Wiley & Sons, Inc., 111 River Street, Hoboken, NJ 07030, (201) 748-6011, fax (201) 748-6008.

Limit of Liability/Disclaimer of Warranty: While the publisher and author have used their best efforts in preparing this book, they make no representation or warranties with respect to the accuracy or completeness of the contents of this book and specifically disclaim any implied warranties of merchantability or fitness for a particular purpose. No warranty may be created or extended by sales representatives or written sales materials. The advice and strategies contained herein may not be suitable for your situation. You should consult with a professional where appropriate. Neither the publisher nor author shall be liable for any loss of profit or any other commercial damages, including but not limited to special, incidental, consequential, or other damages.

For general information on our other products and services please contact our Customer Care Department within the U.S. at 877-762-2974, outside the U.S. at 317-572-3993 or fax 317-572-4002.

Wiley also publishes its books in a variety of electronic formats. Some content that appears in print, however, may not be available in electronic format.

#### Library of Congress Cataloging-in-Publication Data:

Säckinger, Eduard, 1959–

Broadband circuits for optical fiber communication / Eduard Säckinger.

p. cm.

Includes bibliographical references and index.

ISBN 0-471-71233-7 (cloth)

1. Fiber optics. 2. Optical communications.—Equipment and supplies. 3. Broadband amplifiers. 4. Integrated circuits, Very large scale integration. I. Title.

TK7871.58.B74S23 2005 621.383'75---dc22

2004060617

Printed in the United States of America

10 9 8 7 6 5 4 3 2 1

To my wife, Hye-Sun

This Page Intentionally Left Blank

### Preface

This book is the result of lecturing on "Broadband Circuits for Optical Fiber Communication" over the past several years (at Agere Systems and Lucent Technologies seminars; VLSI Symposium, June 2000; MEAD Microelectronics, 2001–2002). During this period, I experimented with various ways of presenting the material and eventually settled on the structure used for this book, which I found worked best. Compared with the lectures, which were limited to just a few hours, this book permits me to go into more detail and to provide many more examples.

*Scope.* We discuss five types of broadband circuits: transimpedance amplifiers, limiting amplifiers, automatic gain control (AGC) amplifiers, laser drivers, and modulator drivers. Some background information about optical fiber, photodetectors, lasers, and modulators is provided to elucidate the system environment in which these circuits operate. A summary of receiver theory is given at the outset to streamline the discussion of the receiver circuits in the later chapters.

For each of the five circuit types, I proceed as follows. First, the main specifications are explained and illustrated with example numerical values. In many IC design projects, a significant amount of time is spent determining the right specifications for the new design. Therefore, emphasis is put on how these specs relate to the system performance. Next, the circuit concepts are discussed in a general manner. At this point, we try to abstract as much as possible from specific semiconductor technologies, bit rates, and so forth. Then, these general concepts are illustrated with practical implementations taken from the literature. A broad range of circuits in

MESFET, HFET, BJT, HBT, BiCMOS, and CMOS technologies are covered. Finally, a brief overview of product examples and current research topics are given.

The focus of this book is on circuits for digital, continuous-mode transmission, which are used, for example, in SONET, SDH, and Gigabit Ethernet applications. Furthermore, we concentrate on high-speed circuits in the range of 2.5 to 40 Gb/s, typically used in long-haul and metro networks. Circuits for burst-mode transmission, which are used, for example, in passive optical networks (PON), as well as analog receiver and transmitter circuits, which are used, for example, in hybrid fiber-coax (HFC) cable-TV systems, also are discussed.

It is assumed that the reader is familiar with basic analog IC design as presented, for example, in *Analysis and Design of Analog Integrated Circuits* by P. R. Gray and R. G. Meyer [34] or a similar book [7, 57].

Style and Audience. My aim has been to present an overview of the field, with emphasis on an intuitive understanding. Many references to the literature are made throughout this book to guide the interested reader to a more complete and in-depth treatment of the various topics. In general, the mindset and notation used are those of an electrical engineer. For example, whenever possible we use voltages and currents rather than abstract variables, we use one-sided spectral densities as they would appear on a spectrum analyzer, we prefer the use of noise bandwidths over Personick integrals, and so forth. Examples are given frequently to make the material more concrete. Many problems, together with their answers, are provided for the reader who wants to practice and deepen his understanding of the learned material. The problem and answer sections also serve as a repository for additional material, such as proofs and generalizations that would be too distracting to present in the main text of this overview. I hope this book will be useful to students or professionals who may wish for some survey of this subject without becoming embroiled in too much technical detail.

Acknowledgments. I would like to thank my colleagues at the Bell Laboratories and Agere Systems, from whom I have learned much of what is presented in this book. I also would like to thank Behzad Razavi, who got this book project started by inviting me to the VLSI Symposium 2000 and asking me to present a tutorial on "Broadband Circuits for Optical Fiber Communications," which later evolved into this book with the same title. I am grateful to Vlado Valence, Ibi and Gabor Temes, and all the other people at MEAD Microelectronics who have made teaching in their course a pleasure.

I am deeply indebted to the many reviewers who have given freely of their time to read through the book, in part or in full. In particular, I am most grateful to Behnam Analui, California Institute of Technology; Prof. Hercules Avramopoulos, National Technical University of Athens; Dr. Kamran Azadet, Agere Systems; Dr. Alexandru Ciubotaru, Maxim Integrated Products; Dr. Sherif Galal, Broadcom Corp.; Dr. Yuriy M. Greshishchev, PMC-Sierra Inc.; Prof. Renuka Jindal, Universisty of Louisiana at Lafayette; Dr. Helen H. Kim, MIT Lincoln Laboratory; Dr. Herwig Kogelnik, Bell Laboratories, Lucent Technologies; Dr. Patrik Larsson, utMOST Technologies; Dr. Marc Loinaz, Aeluros Inc.; Dr. Sunderarajan Mohan, Barcelona Design Inc.; Dr. Kwok Ng, Agere Systems; Nicolas Nodenot, National Semiconductor; Dr. Yusuke Ota, Zenko Technologies Inc.; Joe H. Othmer, Agere Systems; Prof. Sung-Min Park, Ewha Women's University, Seoul; Prof. Ken Pedrotti, University of California, Santa Cruz; Prof. Khoman Phang, University of Toronto; Hans Ransijn, Agere Systems; Prof. Behzad Razavi, University of California, Los Angeles; Prof. Hans-Martin Rein, Ruhr-Universität, Bochum, Germany; Fadi Saibi, Agere Systems; Dr. Leilei Song, Agere Systems; Prof. Sorin Voinigescu, University of Toronto; Jim Yoder, Agere Systems; and Dr. Ty Yoon, Intel Corporation.

Finally, I would like to thank my wife, who has endured more than two years of "weekend work" during which I have converted my lecture notes into this book manuscript.

Despite the effort made, there are undoubtedly some mistakes left in this book. If you have any corrections or suggestions, please e-mail them to edi@ieee.org. Thank you!

E. SÄCKINGER

Tinton Falls, New Jersey September 9, 2004 This Page Intentionally Left Blank

### **Contents**

|   | Preface        |                                             |            |

|---|----------------|---------------------------------------------|------------|

| 1 | Intro          | oduction                                    | 1          |

| 2 | Optical Fiber  |                                             |            |

|   | 2.1            | Loss and Bandwidth                          | 11         |

|   | 2.2            | Dispersion                                  | 14         |

|   | 2.3            | Nonlinearities                              | 18         |

|   | 2.4            | Pulse Spreading due to Chromatic Dispersion | 19         |

|   | 2.5            | Summary                                     | 22         |

|   | 2.6            | Problems                                    | 23         |

| 3 | Photodetectors |                                             | 25         |

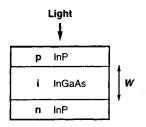

|   | 3.1            | p-i-n Photodetector                         | 25         |

|   | 3.2            | Avalanche Photodetector                     | 31         |

|   | 3.3            | p-i-n Detector with Optical Preamplifier    | 34         |

|   | 3.4            | Summary                                     | <b>4</b> 0 |

|   | 3.5            | Problems                                    | 42         |

xi

| 4 | Rece                            | iver Fu                       | ndamentals                                 | 45  |  |

|---|---------------------------------|-------------------------------|--------------------------------------------|-----|--|

|   | 4.1                             | Receiv                        | ver Model                                  | 45  |  |

|   | 4.2                             | Bit-Er                        | rror Rate                                  | 47  |  |

|   | 4.3                             | Sensit                        | ivity                                      | 54  |  |

|   | 4.4                             |                               |                                            |     |  |

|   | 4.5                             | 0                             |                                            |     |  |

|   | 4.6                             | 5                             |                                            |     |  |

|   | 4.7                             | Adaptive Equalizer            |                                            |     |  |

|   | 4.8                             | Nonlinearity                  |                                            |     |  |

|   | 4.9                             | ) Jitter                      |                                            |     |  |

|   | 4.10 Decision Threshold Control |                               |                                            |     |  |

|   | 4.11                            | 4.11 Forward Error Correction |                                            |     |  |

|   | 4.12                            | 4.12 Summary                  |                                            |     |  |

|   | 4.13                            | Proble                        | ems                                        | 101 |  |

| 5 | Transimpedance Amplifiers       |                               |                                            |     |  |

|   | 5.1                             | •                             | pecifications                              | 105 |  |

|   |                                 | 5.1.1                         | -                                          | 105 |  |

|   |                                 | 5.1.2                         | •                                          | 107 |  |

|   |                                 | 5.1.3                         | Maximum Input Current for Linear Operation | 108 |  |

|   |                                 | 5.1.4                         |                                            | 108 |  |

|   |                                 | 5.1.5                         | Bandwidth and Group-Delay Variation        | 111 |  |

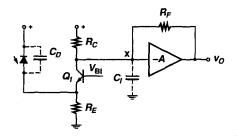

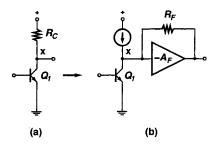

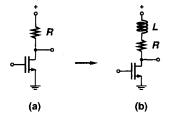

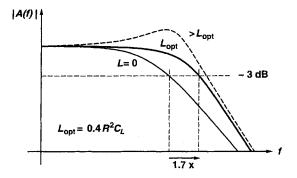

|   | 5.2                             | TIA C                         | ircuit Concepts                            | 112 |  |

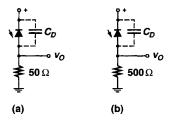

|   |                                 | 5.2.1                         | Low- and High-Impedance Front-Ends         | 112 |  |

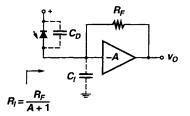

|   |                                 | 5.2.2                         | Shunt Feedback TIA                         | 113 |  |

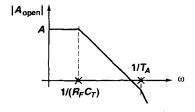

|   |                                 | 5.2.3                         | Noise Optimization                         | 121 |  |

|   |                                 | 5.2.4                         | Adaptive Transimpedance                    | 130 |  |

|   |                                 | 5.2.5                         | Post Amplifier                             | 132 |  |

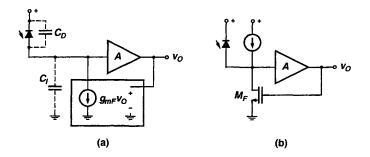

|   |                                 | 5.2.6                         | Common-Base/Gate Input Stage               | 133 |  |

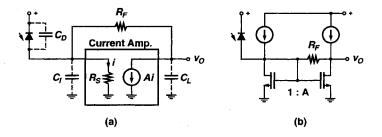

|   |                                 | 5.2.7                         | Current-Mode TIA                           | 134 |  |

|   |                                 | 5.2.8                         | Active-Feedback TIA                        | 135 |  |

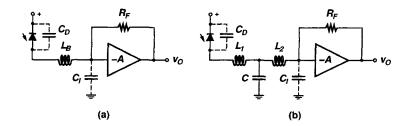

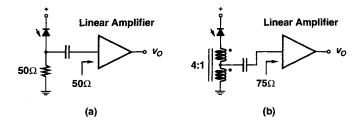

|   |                                 | 5.2.9                         | Inductive Input Coupling                   | 136 |  |

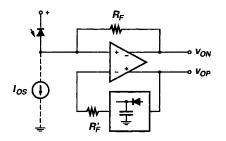

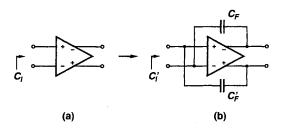

|   |                                 | 5.2.10                        | Differential TIA and Offset Control        | 137 |  |

|   |                                 | 5.2.11                        | Burst-Mode TIA                             | 141 |  |

|   |                                 | 5.2.12                        | Analog Receiver                            | 143 |  |

|   | 5.3                             | TIA Ci                        | ircuit Implementations                     | 145 |  |

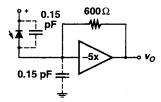

|   |                                 | 5.3.1                         | MESFET and HFET Technology                 | 145 |  |

|   |                                 | 5.3.2                         | BJT, BiCMOS, and HBT Technology            | 147 |  |

|   |                                 | 5.3.3                         | CMOS Technology                            | 149 |  |

5.3.3 CMOS Technology

|   | 5.4                                    | Product Examples                          |            |

|---|----------------------------------------|-------------------------------------------|------------|

|   | 5.5 Research Directions<br>5.6 Summary |                                           |            |

|   |                                        |                                           |            |

|   | 5.7                                    | Problems                                  | 154<br>156 |

| 6 | Mai                                    | Main Amplifiers                           |            |

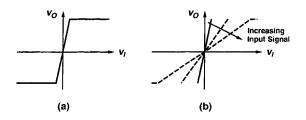

|   | 6.1                                    | Limiting vs. Automatic Gain Control (AGC) | 159        |

|   | 6.2                                    | MA Specifications                         |            |

|   |                                        | 6.2.1 Gain                                | 161        |

|   |                                        | 6.2.2 Bandwidth and Group-Delay Variation | 164        |

|   |                                        | 6.2.3 Noise Figure                        | 165        |

|   |                                        | 6.2.4 Input Dynamic Range                 | 169        |

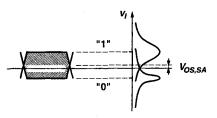

|   |                                        | 6.2.5 Input Offset Voltage                | 171        |

|   |                                        | 6.2.6 Low-Frequency Cutoff                | 173        |

|   |                                        | 6.2.7 AM-to-PM Conversion                 | 175        |

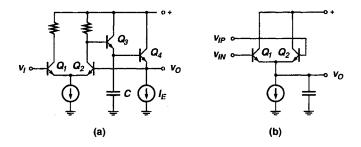

|   | 6.3                                    | MA Circuit Concepts                       |            |

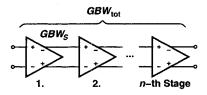

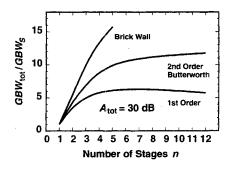

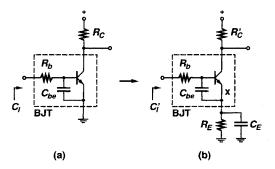

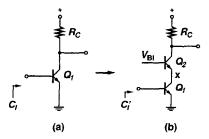

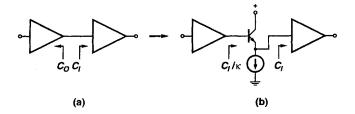

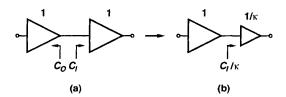

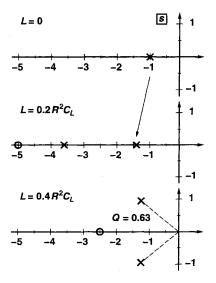

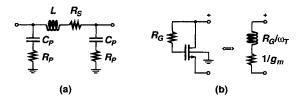

|   |                                        | 6.3.1 Multistage Amplifier                | 176        |

|   |                                        | 6.3.2 Techniques for Broadband Stages     | 179        |

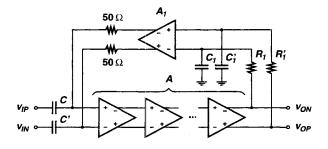

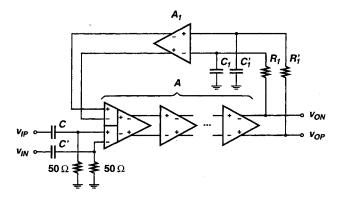

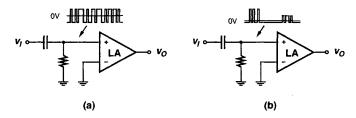

|   |                                        | 6.3.3 Offset Compensation                 | 203        |

|   |                                        | 6.3.4 Automatic Gain Control              | 207        |

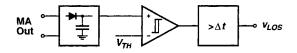

|   |                                        | 6.3.5 Loss of Signal Detection            | 211        |

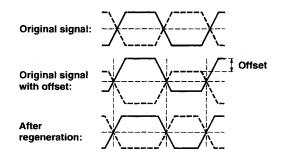

|   |                                        | 6.3.6 Burst-Mode Amplifier                | 212        |

|   | 6.4                                    | MA Circuit Implementations                | 213        |

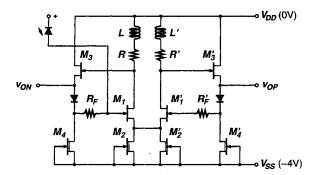

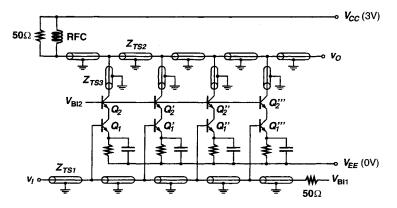

|   |                                        | 6.4.1 MESFET and HFET Technology          | 213        |

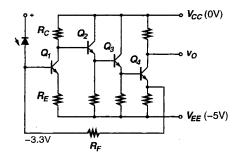

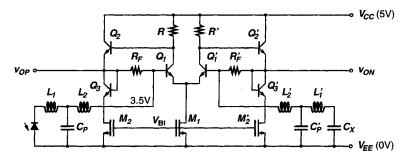

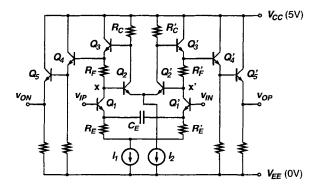

|   |                                        | 6.4.2 BJT and HBT Technology              | 215        |

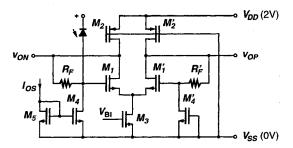

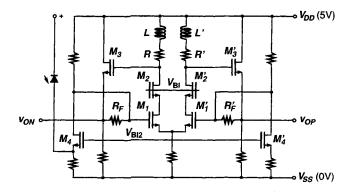

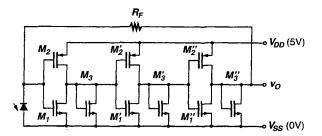

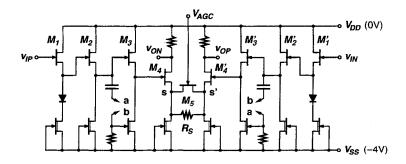

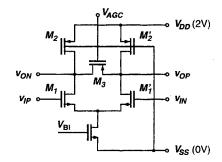

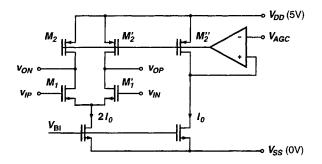

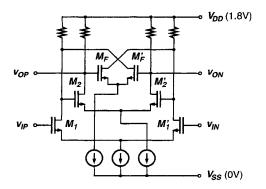

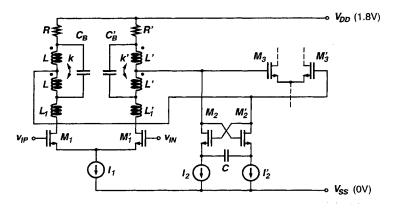

|   |                                        | 6.4.3 CMOS Technology                     | 221        |

|   | 6.5                                    |                                           | 224        |

|   | 6.6                                    | Research Directions                       | 226        |

|   | 6.7                                    | Summary                                   | 227        |

|   | 6.8                                    | Problems                                  | 228        |

| 7 | Opti                                   | Optical Transmitters                      |            |

|   | 7.1 Transmitter Specifications         |                                           | 234        |

|   | 7.2                                    | Lasers                                    | 237        |

|   | 7.3                                    | Modulators                                | 247        |

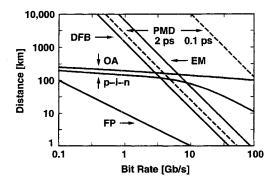

|   | 7.4                                    | Limits in Optical Communication Systems   | 253        |

|   | 7.5                                    | Summary                                   | 256        |

|   | 7.6                                    | Problems                                  | 257        |

| 8  | Laser and Modulator Drivers |         | 259                                  |     |

|----|-----------------------------|---------|--------------------------------------|-----|

|    | 8.1 Driver Specifications   |         |                                      | 259 |

|    |                             | 8.1.1   | Modulation and Bias Current Range    |     |

|    |                             |         | (Laser Drivers)                      | 259 |

|    |                             | 8.1.2   | Output Voltage Range (Laser Drivers) | 261 |

|    |                             | 8.1.3   | Modulation and Bias Voltage Range    |     |

|    |                             |         | (Modulator Drivers)                  | 261 |

|    |                             | 8.1.4   |                                      | 263 |

|    |                             | 8.1.5   |                                      | 264 |

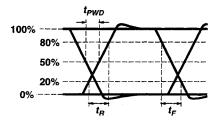

|    |                             | 8.1.6   | Pulse-Width Distortion               | 265 |

|    |                             | 8.1.7   | Jitter Generation                    | 265 |

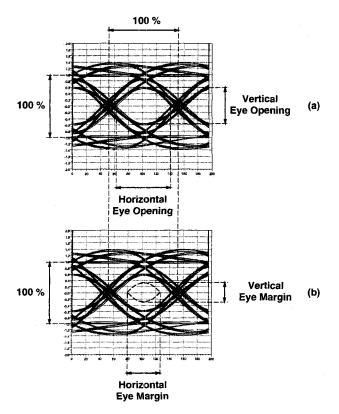

|    |                             | 8.1.8   | Eye-Diagram Mask Test                | 267 |

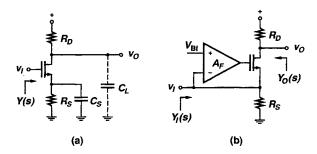

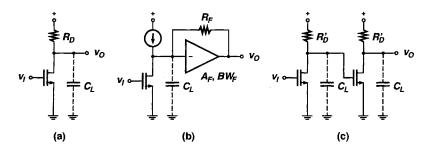

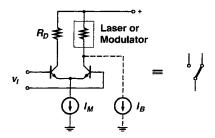

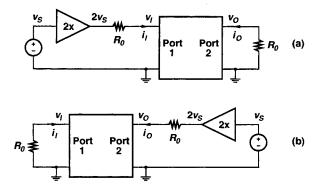

|    | 8.2                         | Driver  | r Circuit Concepts                   | 268 |

|    |                             | 8.2.1   | Current-Steering Output Stage        | 268 |

|    |                             | 8.2.2   | Back Termination                     | 273 |

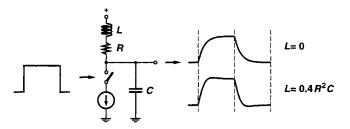

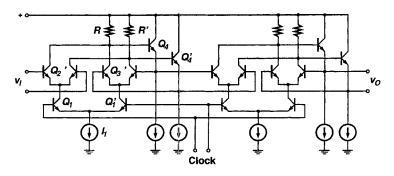

|    |                             | 8.2.3   | Predriver                            | 276 |

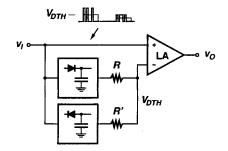

|    |                             | 8.2.4   | Pulse-Width Control                  | 279 |

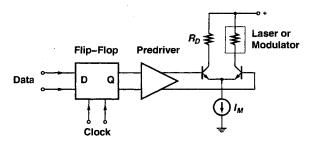

|    |                             | 8.2.5   | Data Retiming                        | 280 |

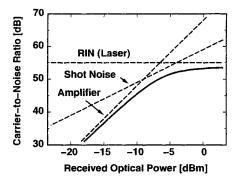

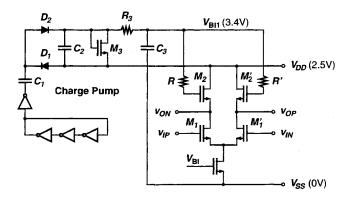

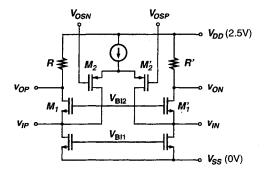

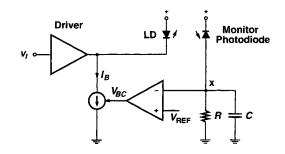

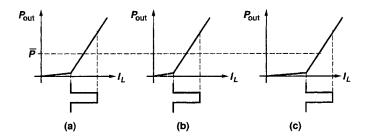

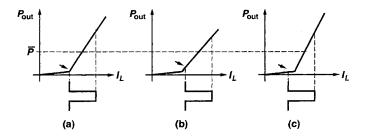

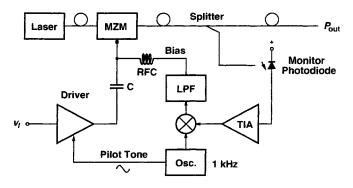

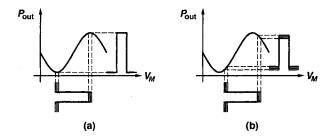

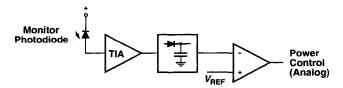

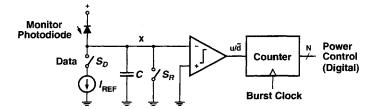

|    |                             |         | Automatic Power Control (Lasers)     | 282 |

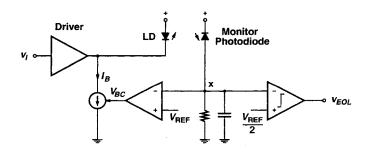

|    |                             |         | End-of-Life Detection (Lasers)       | 285 |

|    |                             | 8.2.8   |                                      | 286 |

|    |                             | 8.2.9   | Burst-Mode Laser Driver              | 287 |

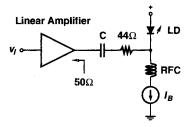

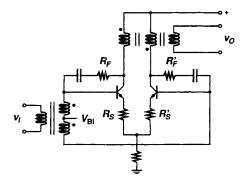

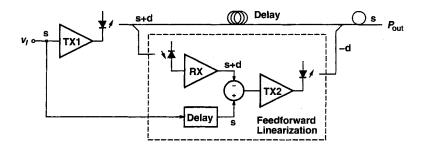

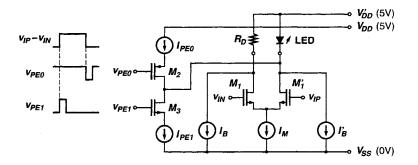

|    |                             | 8.2.10  | Analog Laser/Modulator Driver        | 290 |

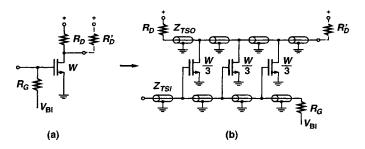

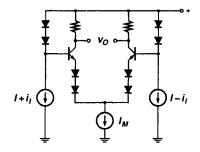

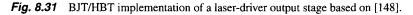

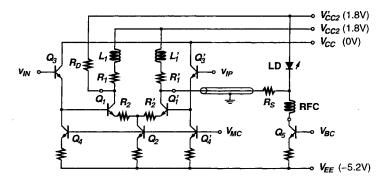

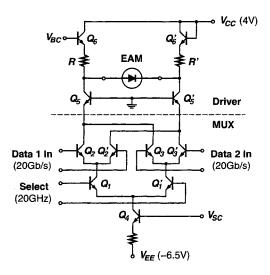

|    | 8.3                         | Driver  | r Circuit Implementations            | 294 |

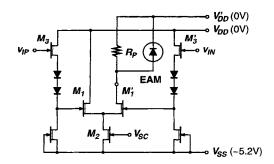

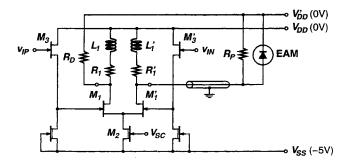

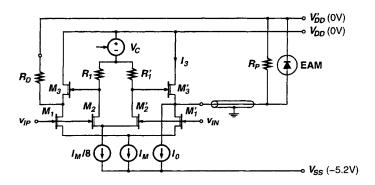

|    |                             | 8.3.1   | -                                    | 294 |

|    |                             | 8.3.2   |                                      | 297 |

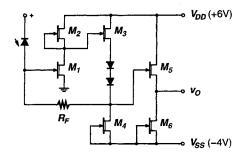

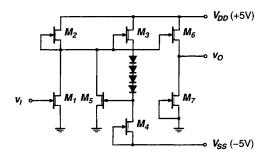

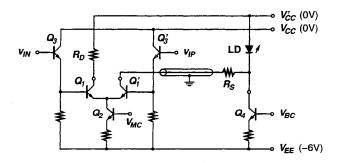

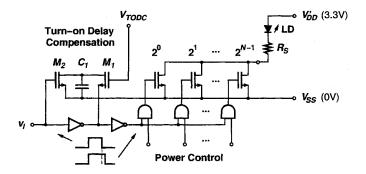

|    |                             | 8.3.3   | CMOS Technology                      | 302 |

|    | 8.4                         | Produ   | ct Examples                          | 305 |

|    | 8.5                         | •       |                                      | 305 |

|    | 8.6                         | Summary |                                      | 308 |

|    | 8.7                         | Proble  | ems                                  | 309 |

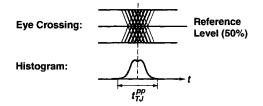

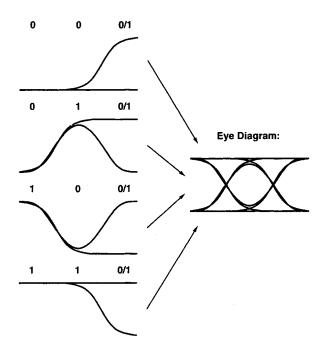

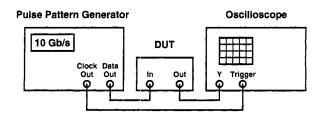

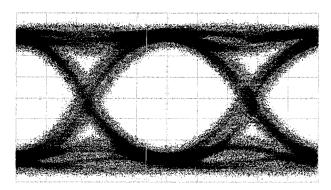

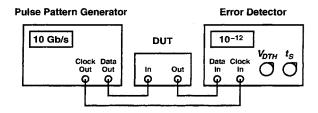

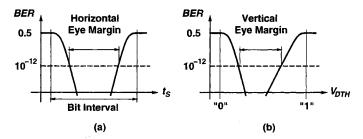

| Ap | pendi                       | x A Eye | e Diagrams                           | 313 |

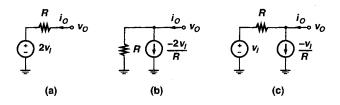

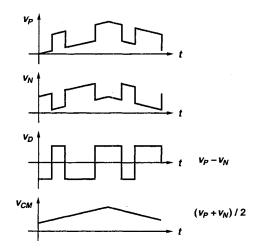

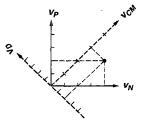

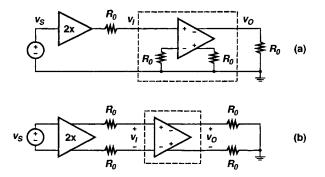

| Ap | pendi                       | x B Dit | fferential Circuits                  | 321 |

|    | B.1                         |         | ential Mode and Common Mode          | 322 |

|    | <b>B</b> .2                 | 00      | odes of Currents and Impedances      | 324 |

|    |                             |         |                                      |     |

B.3 Common-Mode and Power-Supply Rejection 325

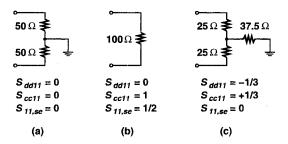

| Appendix C S Parameters                     | 329         |

|---------------------------------------------|-------------|

| C.1 Definition and Simulation               | 329         |

| C.2 Matching Considerations                 | 333         |

| C.3 Differential S Parameters               | 339         |

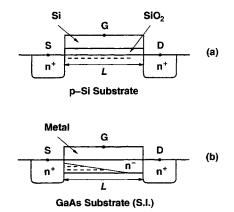

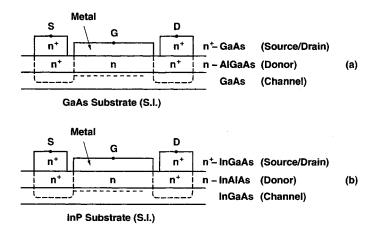

| Appendix D Transistors and Technologies     | 343         |

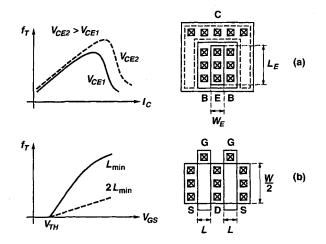

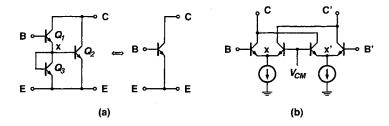

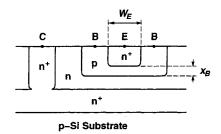

| D.1 MOSFET and MESFET                       | 343         |

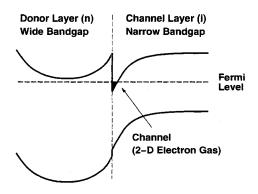

| D.2 Heterostructure FET (HFET)              | <i>34</i> 8 |

| D.3 Bipolar Junction Transistor (BJT)       | 351         |

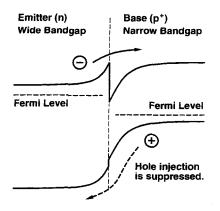

| D.4 Heterojunction Bipolar Transistor (HBT) | 355         |

| Appendix E Answers to the Problems          | 359         |

| Appendix F Notation                         | 385         |

| Appendix G Symbols                          | 387         |

| Appendix H Acronyms                         | 399         |

| References                                  | 407         |

| Index                                       | 425         |

This Page Intentionally Left Blank

## <u>I</u> Introduction

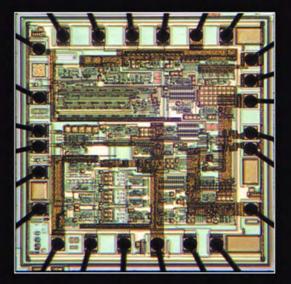

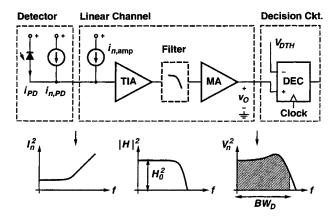

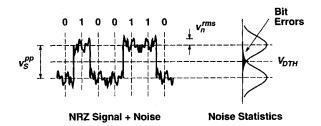

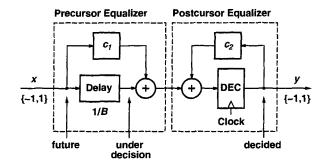

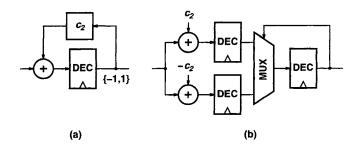

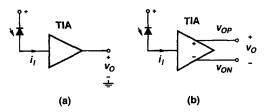

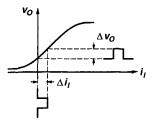

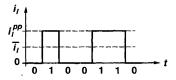

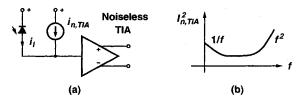

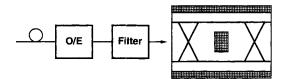

Optical Receiver and Transmitter. Figure 1.1 shows the block diagram of a typical optical receiver and transmitter. The optical signal from the fiber is received by a photodetector (PD), which produces a small output current proportional to the optical signal. This current is amplified and converted to a voltage by a transimpedance amplifier (TIA or TZA). The voltage signal is amplified further by either a *limiting* amplifier (LA) or an automatic gain control amplifier (AGC amplifier). The LA and AGC amplifier are collectively known as main amplifiers (MAs) or post amplifiers. The resulting signal, which is now several 100 mV strong, is fed into a clock and data recovery circuit (CDR), which extracts the clock signal and retimes the data signal. In high-speed receivers, a demultiplexer (DMUX) converts the fast serial data stream into n parallel lower-speed data streams that can be processed conveniently by the digital logic block. Some CDR designs (those with a parallel sampling architecture) perform the DMUX task as part of their functionality, and an explicit DMUX is not needed in this case [47]. The digital logic block descrambles or decodes the bits, performs error checks, extracts the payload data from the framing information, synchronizes to another clock domain, and so forth. The receiver just described also is known as a 3R receiver because it performs signal re-amplification in the TIA (and the AGC amplifier, if present), signal *re-shaping* in the LA or CDR, and signal re-timing in the CDR.

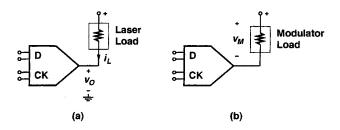

On the transmitter side, the same process happens in reverse order. The parallel data from the digital logic block are merged into a single high-speed data stream using a *multiplexer* (MUX). To control the select lines of the MUX, a bit-rate (or half-rate) clock must be synthesized from the slower word clock. This task is performed by a *clock multiplication unit* (CMU). Finally, a *laser driver* or *modulator driver* drives

Fig. 1.1 Block diagram of an optical receiver (top) and transmitter (bottom).

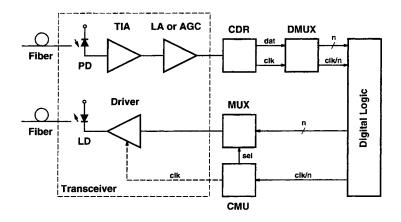

**Fig. 1.2** A 2.5-Gb/s transceiver in a "small form-factor pluggable" (SFP) package  $(5.7 \text{ cm} \times 1.4 \text{ cm} \times 1.1 \text{ cm})$ . The two fibers are plugged in from the left (LC connectors). Reprinted by permission from Agere Systems, Inc.

the corresponding optoelectronic device. The laser driver modulates the current of a *laser diode* (LD), whereas the modulator driver modulates the voltage across a *modulator*, which in turn modulates the light intensity from a *continuous wave* (CW) laser. Some laser/modulator drivers also perform data retiming, and thus require a bit-rate (or half-rate) clock from the CMU (dashed line in Fig. 1.1).

A module containing a PD, TIA, MA, laser driver, and LD, that is, all the blocks shown inside the dashed box of Fig. 1.1, often is referred to as a *transceiver*.<sup>1</sup> See Fig. 1.2 for a so-called *small form-factor* transceiver module. A module that contains all the functionality of the transceiver plus a CDR, DMUX, CMU, and MUX frequently is called a *transponder*. In this book, we discuss the PD, TIA, MA, as well as the laser/modulator and their drivers in greater detail.

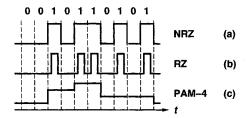

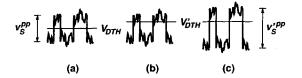

**Modulation Schemes.** The most commonly used modulation format in optical communication is the *non-return-to-zero* (NRZ) format shown in Fig. 1.3(a). This format is a form of *on-off keying* (OOK): the signal is *on* to transmit a one bit and is *off* to transmit a zero bit. When the signal (i.e., the laser light) is on, it stays on for the entire bit period. For example, when transmitting the periodic bit pattern "010101010..." at 10 Gb/s in NRZ format, a 5-GHz square wave with 50% duty cycle is produced.<sup>2</sup>

Fig. 1.3 Modulation schemes: (a) NRZ, (b) RZ, and (c) PAM-4.

In high-speed and long-haul transmission (e.g., fiber links between two continents), the *return-to-zero* (RZ) format, shown in Fig. 1.3(b), generally is preferred. In this format, the pulses, which represent the one bits, occupy only a fraction (e.g., 50%) of the bit period. Compared with the NRZ signal, the RZ signal requires less signal-to-noise ratio for reliable detection but occupies a larger bandwidth because of its shorter pulses.<sup>3</sup> An important advantage of this narrow-pulse format is that more pulse distortion and spreading can be tolerated without disturbing the adjacent bits.

<sup>&</sup>lt;sup>1</sup>The term *transceiver* is a contraction of the words "transmitter" and "receiver".

$<sup>^{2}</sup>$ In some standards, such as Fast Ethernet and FDDI, the *non-return-to-zero change-on-ones* (NRZ1 or NRZI) format is used. This format also is based on NRZ modulation, but before modulation, the bit stream is passed through a line coder that changes its (binary) output value when the bit to be transmitted is a one and leaves the output value unchanged when the bit is a zero.

$<sup>^{3}</sup>$ To receive data at a bit-error rate of  $10^{-12}$ , we need a signal-to-noise ratio of 16.9 dB for NRZ modulation, 15.7 dB for 50%-RZ modulation, and 23.9 dB for PAM-4 modulation assuming additive Gaussian noise

Thus, this format is more immune to effects of fiber nonlinearity and polarizationmode dispersion. On the downside, faster, more expensive transceiver components (laser/modulator, photodetector, front-end electronics, etc.) are required to handle the shorter pulses. Furthermore, in optical multichannel systems, the wavelengths can be packed less densely because the RZ signal occupies a wider bandwidth than the NRZ signal for a given bit rate. Several variations of the RZ modulation, such as the *chirped return-to-zero* (CRZ) modulation, the *carrier-suppressed return-to-zero* (CS-RZ) modulation, and the *return-to-zero differential phase-shift keying* (RZ-DPSK) modulation also are used, but a discussion of these modulation schemes is beyond the scope of this book.

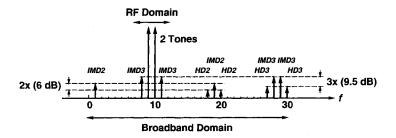

Since the late 1980s, the TV signals in *community-antenna television* (CATV) systems often are transported first *optically* from the distribution center to the neighborhood before they are distributed to the individual homes on conventional coaxial cable. This combination, called *hybrid fiber-coax* (HFC), has the advantage over an all-coax system in that it saves many electronic amplifiers (the loss in a fiber is much lower than the loss in a coax cable) and provides better signal quality (lower noise and distortions). In the optical part of the HFC system, the laser light is modulated with multiple radio-frequency (RF) carriers, so-called subcarriers, each one corresponding to a different TV channel. This method is known as *subcarrier multiplexing* (SCM).<sup>4</sup> Then, each subcarrier is modulated with a TV signal, for example, *amplitude modulation with vestigial sideband* (AM-VSB) is used for analog TV channels and *quadrature amplitude modulation* (QAM) is used for digital TV channels.

In contrast to NRZ and RZ modulation, which produce a two-level digital signal (laser light on or off), the AM-VSB and QAM modulation used in CATV applications produce continuous or multilevel analog signals. Figure 1.3(c) illustrates a multilevel signal produced by *pulse amplitude modulation* (PAM), a modulation scheme that is related to QAM. In this example, groups of two successive bits are encoded with one of four signal levels, and hence this format is known as PAM-4. Compared with the NRZ signal, the PAM-4 signal requires a higher signal-to-noise ratio for reliable detection but occupies a narrower bandwidth because its symbol rate is only half the bit rate. Similarly, the analog signals distributed over CATV/HFC systems require a high signal-to-noise ratio and transceivers with a good linearity to minimize distortions.

In the remainder of this book, we always assume that we are dealing with NRZ modulation, except if stated otherwise, as, for example, in the sections on analog receiver and transmitter circuits.

*Line Codes.* Before data bits are modulated onto the optical carrier, they usually are preconditioned with a so-called *line code*. The line code provides the transmitted bit stream with the following desirable properties: *DC balance*, short *run lengths*,

<sup>(</sup>cf. Problems 4.4 and 4.6). The signal bandwidth measured from DC to the first null is B for NRZ modulation, 2B for 50%-RZ modulation, and B/2 for PAM-4 modulation, where B is the bit rate.

<sup>&</sup>lt;sup>4</sup>In contrast to *discrete multitone* (DMT) modulation (or *orthogonal frequency division multiplexing* [OFDM], the RF modulated equivalent), which uses overlapping channel spectra, SCM keeps a frequency gap between the channels.

and a high *transition density*. A DC balanced bit stream contains the same number of zeros and ones on average. This is equivalent to saying that the average *mark density* (number of one bits divided by all bits) is 50%. A DC balanced signal has the nice property that its average value (the DC component) is always centered halfway between the zero and one levels (half of the peak-to-peak value). This property often permits the use of AC coupling between circuit blocks, simplifying their design. Furthermore, it is desirable to keep the number of successive zeros and ones, the run length, to a small value. This provision reduces the low-frequency content of the transmitted signal and limits the associated *baseline wander* (a.k.a. *DC wander*) when AC coupling is used. Finally, a high transition density is desirable to simplify the clock recovery process.

In practice, line coding is implemented as either *scrambling*, *block coding*, or a combination of the two:

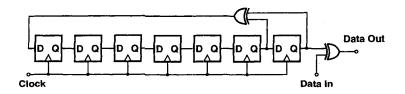

• Scrambling. In this case, a pseudorandom bit sequence (PRBS) is generated with a feedback shift register and xor'ed with the data bit stream (see Fig. 1.4). Note that the data can be descrambled with the same arrangement, provided the descrambling PRBS generator is synchronized with the scrambling PRBS generator. Scrambling provides DC balance without adding overhead bits to the bit stream, thus preserving the bit rate. On the down side, the maximum run length is not strictly limited, that is, there is a small chance for very long runs of zeros or ones, which can be hazardous. In practice, runs up to 72 bits usually are expected. The scrambling method is used in the United States telecommunication system described in the SONET (synchronous optical network) standard [188] and the almost identical SDH (synchronous digital hierarchy) standard used in Europe and Japan.

Fig. 1.4 Implementation of a SONET scrambler.

• *Block Coding*. In this case, a contiguous group of bits (a block) is replaced by another slightly larger group of bits such that the average mark density becomes 50% and DC balance is established. For example, in the 8B10B code, 8-bit groups are replaced with 10-bit patterns using a look-up table [198]. The 8B10B code increases the bit rate by 25%; however, the maximum run length is strictly limited to five zeros or ones in a row. The 8B10B code is used in the

#### 6 INTRODUCTION

Gigabit Ethernet (GbE, 1000Base-SX, 1000Base-LX) and Fiber Channel data communication systems.<sup>5</sup>

• Combination. In the serial 10-Gigabit Ethernet (10-GbE) system, DC balance is established first by scrambling the bit stream and then by applying a block-code (64B66B code) to it. This combination features low overhead ( $\approx 3\%$  increase in bit rate) and a run length that is strictly limited to 66 bits.

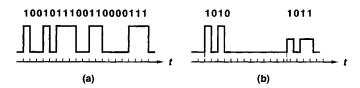

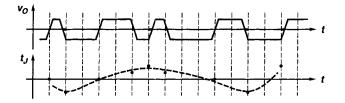

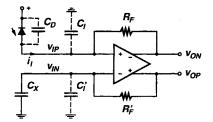

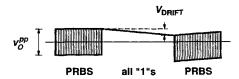

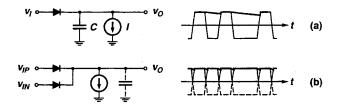

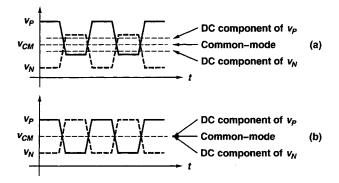

Continuous Mode vs. Burst Mode. It is important to distinguish two types of transmission modes because they call for different circuit designs: continuous mode and burst mode. The signals corresponding to these two modes are shown schematically in Fig. 1.5.

Fig. 1.5 (a) Continuous-mode vs. (b) burst-mode signals (schematically).

In continuous-mode transmission, a continuous, uninterrupted stream of bits is transmitted as shown in Fig. 1.5(a). The transmitted signal usually is DC balanced using one of the line codes described earlier. As a result, AC coupled circuits normally can be used. In burst-mode transmission, data are transmitted in short *bursts*, with the transmitter remaining silent (laser off) in between bursts. See Fig. 1.5(b) for an illustration, but note that practical bursts are much longer than those shown in the figure, typically longer than 400 bits.

Bursts can be fixed or can be variable in length. Bursts that encode ATM (asynchronous transfer mode) cells have a *fixed length*, they always contain 53 bytes plus a preamble (e.g., 3 bytes). Bursts that encode Ethernet frames have a *variable length* (70–1524 bytes). In either case, the bursts start out with a preamble (a.k.a. overhead) followed by the payload. The burst-mode receiver uses the preamble to establish the decision threshold level (slice level) and to synchronize the receiver clock. In passive optical network systems, to be discussed shortly, bursts arrive *asynchronously* and with strongly *varying power levels* (up to 30 dB); therefore, the clock signal must be synchronized and the slice level adjusted for every single burst (cf. Fig. 1.5(b)).

The average value (DC component) of a burst-mode signal varies with time, depending on the burst activity. If the activity is high, it may be close to the halfway point between the zero and one levels, as in a continuous mode system; if the activity is low, the average drifts arbitrarily close to the zero level. This means that the burstmode signal is *not* DC balanced, and in general, AC coupling cannot be used because

<sup>&</sup>lt;sup>5</sup>The 4B5B code used in Fast Ethernet (100Base-TX, 100Base-FX), FDDI, and so forth, does not achieve perfect DC balance; the worst-case unbalance is 10% [136].

it would lead to excessive baseline wander. (Note that the mark density within a *burst* may well be 50%, but the overall signal is still not DC balanced.) This lack of DC balance and the fact that bursts often arrive with varying amplitudes necessitate specialized amplifier and driver circuits for burst-mode applications. Furthermore, the asynchronous arrival of the bursts requires specialized fast-locking CDRs.

In the remainder of this book we always assume that we are dealing with DCbalanced, continuous-mode signals, except if stated otherwise, as, for example, in the sections on burst-mode circuits.

**Optical Networks.** We must distinguish two important types of optical networks: the simple *point-to-point connection* and the *point-to-multipoint network*. In the following, we discuss these networks and how continuous-mode and burst-mode transmissions are used with them.

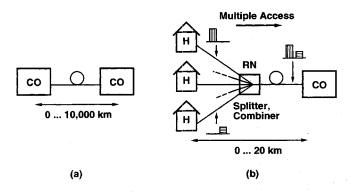

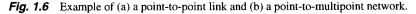

An optical point-to-point connection between two *central offices* (CO) is illustrated schematically in Fig. 1.6(a). An example for such a connection is a SONET OC-192 link operating at 10 Gb/s (9.953 28 Gb/s to be precise), a bit rate that can carry about 130,000 voice calls. Point-to-point links are used over a wide range of bit rates and distances, from short computer-to-computer links to ultra-long-haul undersea lightwave systems.

Point-to-point connections can be assembled into more complex structures such as *ring networks* and *active star networks*. Examples for ring networks are provided by SONET/SDH rings and FDDI token rings. An active star is formed, for example, by Gigabit Ethernet links converging into a hub. It is important to realize that each individual optical connection of the star has a transceiver on both ends and therefore forms an optical point-to-point link. This is in contrast to a *passive star network* or an optical point-to-multipoint network, where multiple optical fibers are coupled with a passive optical device. We discuss the latter network type below.

Continuous-mode transmission is used on almost all point-to-point connections. One exception occurs in half-duplex systems, in which bidirectional communication is implemented by periodically reversing the direction of traffic following a pingpong pattern, so-called *time compression multiplexing* (TCM; a.k.a. *time division duplexing*). Such systems require burst-mode transmitters and receivers. However, for bandwidth efficiency reasons, TCM systems are limited to relatively short links (e.g., home networking applications) and are not widely used. In all other cases of bidirectional transmission, for example, with two fibers, so-called *space division multiplexing* (SDM), or two wavelengths, so-called *wavelength division multiplexing* (WDM), continuous-mode transmission is used.

**Passive Optical Network.** A passive optical network (PON) is illustrated schematically in Figure 1.6(b). A feeder fiber from the central office (CO) runs to a remote node (RN), which houses a passive optical power splitter/combiner. From there, around 32 fibers branch out to the subscribers. If these fibers extend all the way to the homes (H), as shown in Fig 1.6(b), this system is known as a fiber-to-the-home (FTTH) system. Alternatively, if the fibers terminate at the curb, the system is known as a fiber-to-the-curb (FTTC) system. The final distribution from the curb to the homes is accomplished, for example, by twisted-pair copper wires or radio. All systems that bring the fiber relatively close to the subscriber are collectively known as FTTx systems.

In a traditional telephony access network, the connection between the CO and the remote node is a digital, possibly optical line. The final distribution from the remote node to the subscribers, however, is accomplished with analog signals over twisted-pair copper wires. Thus, the remote node must be *active*; that is, it needs to be powered to perform the conversion from the high-speed digital signal to the analog signals. In contrast, a PON system is all optical and *passive*. Because a PON does not require outside power supplies, it is low in cost, easy to maintain, and reliable.

A PON is a point-to-multipoint network because the optical medium is *shared* among the subscribers. Information transmitted downstream, from the CO to the subscriber, is received by all subscribers, and information transmitted upstream, from the subscribers to the CO, is superimposed at the passive combiner before it is received at the CO. To avoid data collisions in the *upstream direction*, the subscriber data must be buffered and transmitted in short bursts. The CO must coordinate which subscriber can send a burst at which point in time. This method is known as *time division multiple access* (TDMA) and requires *burst-mode transmission*. The *downstream direction* is more straightforward: the CO tags the data with addresses and broadcasts it to all subscribers in sequential order. Each subscriber simply selects the information with the appropriate address tag. This method is known as *time division multiplexing* (TDM), and conventional continuous-mode transmission can be used. Upstream and downstream transmissions usually are separated by using two different wavelengths (WDM bidirectional transmission).

The most promising PON systems are (i) BPON (broadband passive optical network), which carries the data in ATM cells and hence also is known as ATM-PON [30, 52], and (ii) EPON (Ethernet passive optical network), which carries the data in Ethernet frames, as the name implies [48]. In general, PON FTTx networks are limited to relatively small distances (<20 km) and currently are operated at modest bit rates (50 Mb/s–1.25 Gb/s). In a typical BPON FTTH scenario, 16 to 32 homes share a bit rate of 155 Mb/s, giving each subscriber an average speed of 5 to 10 Mb/s. This is sufficient for fast Internet access, telephone service, and video on demand. Sometimes, an all-optical CATV service is provided over the PON infrastructure by means of a third wavelength.

Besides the TDM/TDMA approach outlined above, there are several other types of PON systems. For example, the WDM-PON system, where a different wavelength is assigned to each subscriber, has been studied extensively. In WDM-PON systems, data collisions are avoided without the need for burst-mode transmission. However, the optical WDM components required for such a system currently are too expensive, making WDM-PON uneconomical. For more information on PON systems see [40, 69].

**Book Outline.** In Chapter 2, we introduce the communication channel presented by the optical fiber. Its loss, bandwidth, and various forms of dispersion are described briefly. The relationship between pulse spreading and transmitter linewidth is given and is used later in Chapter 7.

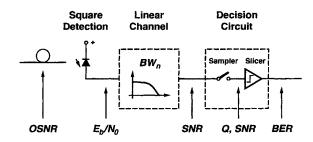

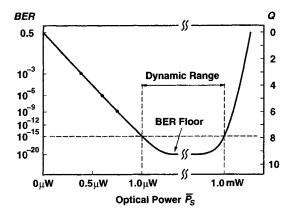

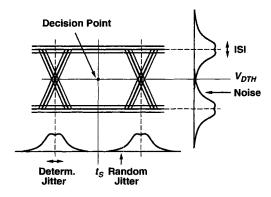

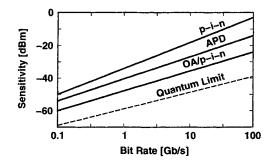

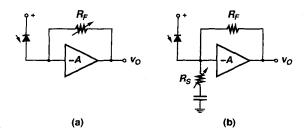

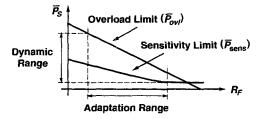

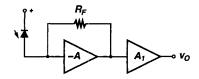

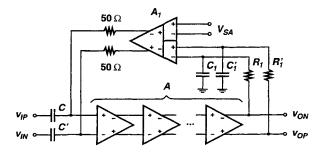

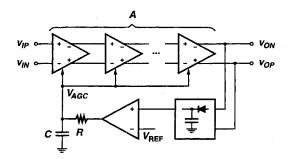

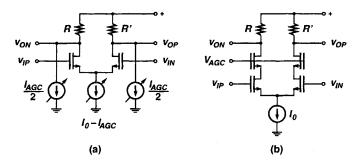

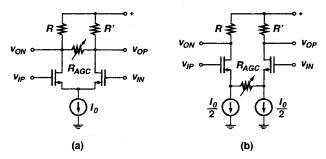

Chapter 3 is the first of four chapters dealing with the receiver. We start by studying the responsivity and noise properties of three photodetector types: the p-i-n photodetector, the avalanche photodetector, and the optically preamplified p-i-n detector. In Chapter 4, we present the receiver at the system level. This chapter introduces terminology and concepts that simplify the discussion in later chapters. First, we analyze how noise in the receiver causes bit errors. This leads to the definition of the receiver sensitivity. Next, after introducing the concept of power penalty, we study the impact of the receiver's bandwidth and frequency response on its performance. The adaptive equalizer, used to mitigate distortions in the received signal, is covered briefly. We then turn to other receiver impairments, such as nonlinearity (in analog receivers), jitter, decision threshold offset, and sampling time offset. We conclude with a brief description of forward error correction, a technique that can improve the receiver's performance dramatically. In Chapter 5, we discuss the transimpedance amplifier. We start by introducing the main specifications. Next, we discuss circuit concepts in a general, and as much as possible, technology independent manner. This includes the shunt-feedback architecture and variations thereof, noise optimization procedures, and special techniques for burst-mode and analog TIAs. Then, we illustrate these concepts with practical implementations in a broad range of technologies. We conclude with a brief overview of product examples and current research topics. In Chapter 6, we discuss the main amplifier, that is, the limiting and AGC amplifier. As in the previous chapter, we proceed from specifications to circuit concepts to implementation examples. The circuit concepts covered include the multistage architecture, techniques for broadband stages, offset compensation, and automatic gain control.

Chapter 7 is the first of two chapters dealing with the transmitter. We start by studying various types of lasers and optical modulators. In Chapter 8, we discuss the driver circuits for directly modulated lasers as well as external modulators. As in Chapters 5 and 6, we proceed from specifications to circuit concepts to implementation examples. The circuit concepts covered include the current-steering output stage with

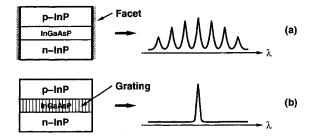

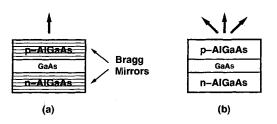

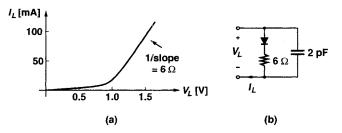

and without back termination, the predriver with pulse-width control, data retiming, automatic power control, and special techniques for burst-mode and analog drivers.

Appendices A through D provide additional material on eye diagrams, differential circuits, S parameters, transistors, and technologies. Answers to all problems are given in Appendix E. The notation for currents, voltages, and noise quantities used in this book is explained in Appendix F. For reference, Appendix G defines all symbols and Appendix H defines all acronyms used in this book.

About Numerical Examples. In the following chapters, we make extensive use of numerical examples. Frequently when we introduce a new quantity or relationship, we illustrate it with so-called *typical values*. In my own learning experience, this approach is most helpful: it makes the subject more concrete and promotes a feeling for the numerical values. However, specialists tend to be quite critical about such values because they are never quite right. Typical values may change over time as the technology advances or they may depend on several conditions that may or may not be met in a particular case. It therefore is important to take the subsequent typical values only as an illustration and not as the basis for your next design project!

Further Reading. The book High-Speed Circuits for Lightwave Communications edited by K. Wang contains an interesting collection of papers discussing many insightful case studies [197]. The textbook Design of Integrated Circuits for Optical Communications by B. Razavi presents an overview of circuits for optical communication, including phase-locked loops and clock and data recovery circuits [141]. The latest developments in integrated circuits for optical communication are published in several magazines and at various conferences, for example, the IEEE Journal of Solid-State Circuits and the IEEE International Solid-State Circuits Conference are excellent sources. Information about optical fibers, lasers, detectors, optical amplifiers, as well as optical networks can be found in the textbooks Fiber-Optic Communication Systems by G. Agrawal [5] and Optical Networks: A Practical Perspective by R. Ramaswami et al. [136]. The continually updated book series Optical Fiber Telecommunications (so far Volumes I-IV have been published) covers the latest developments in optical/optoelectronic components and systems [58, 59, 60, 61, 93]. Finally, I recommend City of Light: The Story of Fiber Optics by Jeff Hecht for an entertaining and informative historical account on fiber optics [43].

**Optical** Fiber

In this chapter, we introduce the communication channel presented by the optical fiber. However, it is well beyond the scope of this book to treat this subject in depth. Therefore, we concentrate here on the main characteristics of optical fiber that will be useful later in this book. In particular, we describe the loss, the bandwidth, and the various forms of fiber dispersion. The relationship between pulse spreading and transmitter linewidth is discussed in preparation for Chapter 7. For a more complete treatment of this subject, many excellent books, such as [5, 136, 168], are available.

#### 2.1 LOSS AND BANDWIDTH

Loss. As the optical signal propagates over a long stretch of fiber, it becomes attenuated because of scattering, absorption by material impurities, and other effects. The attenuation is measured in dBs  $(10 \cdot \log of power ratio)$  and is proportional to the length of the fiber. *Fiber attenuation* or *fiber loss* is therefore specified in dB/km.

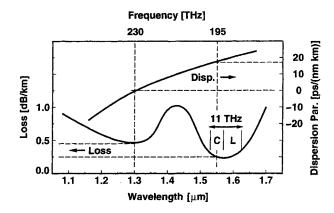

As shown in Fig. 2.1, *silica glass* has two low-loss windows, one around the wavelength  $\lambda = 1.3 \,\mu\text{m}$  and one around  $\lambda = 1.55 \,\mu\text{m}$ , which both are used for optical fiber communication.<sup>1</sup> The popular single-mode fiber has a loss of about 0.25 dB/km at the 1.55- $\mu$ m wavelength and 0.4 dB/km at the 1.3- $\mu$ m wavelength. Because the loss is lower at 1.55  $\mu$ m, this wavelength is preferred for long-haul communication.

<sup>&</sup>lt;sup>1</sup>Note that these wavelengths, and all wavelengths we refer to later, are defined in the *vacuum*. Thus, an optical signal with  $\lambda = 1.55 \,\mu$ m has a wavelength of about 1  $\mu$ m in a glass fiber, which has a refractive index of about 1.5!

A third wavelength window around  $\lambda = 0.85 \,\mu$ m, where the loss is about 2.5 dB/km, is used for short-reach (data) communication applications, mostly because low-cost optical sources and detectors are available for this wavelength.

Fig. 2.1 Loss and dispersion parameter D of a standard single-mode fiber.

The loss of modern silica-glass fiber is phenomenally low compared with that of an RF coax cable at high frequencies. A high-performance RF coax cable operating at 10 GHz has an attenuation of about 500 dB/km. Compare this with 0.25 dB/km for a fiber! On a historical note, it is interesting to know that low-loss fiber was not easy to produce. In 1965, the best glass fiber had a loss of around 1,000 dB/km. It was estimated that for a fiber to be useful for optical communication, its loss must be reduced to 20 dB/km or less, that is, an improvement by 98 orders of magnitude was required!! It is therefore understandable that in '65 most researchers thought that using glass fiber for optical communication was a hopelessly crazy idea. They spent their time working on "reasonable" approaches to optical communication such as metal pipes that contain periodically spaced lenses (so-called *confocal waveguides*) or pipes heated in such a way that the air in them formed gas lenses. Nevertheless, in 1970, a research team at the Corning Glass Works managed to reduce the fiber loss below 20 dB/km by using ultrapure silica glass rather than the ordinary compound glass [43]. So, next time your circuit parameters are off by 98 orders of magnitude, don't give up ...

In comparison with silica glass fiber, *plastic optical fiber* (POF) is very cheap to manufacture and also permits the use of low-cost connectors because of its large core size of almost 1 mm. However, it has a huge loss of about 180 dB/km, even when operated in the "low-loss" window at 0.65  $\mu$ m (visible red). It therefore is restricted to very-short reach applications such as home networks and consumer electronics.

Although the loss of silica glass fiber is very low, it is still not low enough for ultralong-haul communication (e.g., 10,000 km of fiber) without optoelectronic repeaters. What can we do to reduce the loss further? First, we must operate the fiber at the 1.55- $\mu$ m wavelength where loss is the lowest. Then, we can use periodically spaced optical in-line amplifiers to boost the signal and thus effectively reduce the optical loss. Two types of fiber amplifiers are in use: (i) the *erbium-doped fiber amplifier* (EDFA), which provides gain in the 1.55- $\mu$ m band, and (ii) the *Raman amplifier*, which can provide distributed gain in the transmission fiber itself at a selectable wavelength (13 THz below the pump frequency). A third type of fiber amplifier is in the research stage: the *fiber optical parametric amplifier* (FOPA), which promises gain over a very wide bandwidth (e.g., 200 nm) at a selectable wavelength.

**Bandwidth.** In addition to the very low loss, optical fiber also has a huge bandwidth. By bandwidth, we mean the range of optical frequencies or wavelengths for which the fiber is highly transparent. For example, the low-loss window around the 1.55- $\mu$ m wavelength is subdivided into two bands (C band for "conventional" and L band for "long-wavelength"), which together provide a bandwidth of 95 nm, corresponding to about 11 THz (see Fig. 2.1). This means that we can transmit about 4 Tb/s of information over a fiber using the C+L bands and the non-return-to-zero (NRZ) modulation format, which achieves a spectral efficiency of about 0.4 b/s/Hz. For example, a backbone connection consisting of 100 parallel fibers could transport up to 400 Tb/s of information, or a fiber-to-the-home (FTTH) system based on a passive optical network (PON) in which each feeder fiber serves 100 subscribers could be upgraded to 40 Gb/s per user, if the demand should arise! This should be enough access bandwidth for the foreseeable future, and that's why FTTH advocates tout their system as *future proof*. [ $\rightarrow$  Problem 2.1]

Bandwidth and Dispersion. Given that we have more than 10 THz of bandwidth in the fiber, could we take a  $1.55-\mu$ m laser, modulate it with a 4 Tb/s NRZ data stream, and use this arrangement for optical transmission, at least in theory? Besides the fact that the electronic circuits and the optoelectronic devices (laser, detector) would be too slow, the propagation of the optical signal over the fiber would present a major limit! The received signal would be totally distorted already after a very short distance because of *dispersive effects* in the fiber. The transmitted optical signal in our hypothetical system has a very large spectral width, filling all of the C and L band. Although each spectral component is in the low-loss window and arrives intact at the other end of the fiber, each component is delayed by a *different* amount, and the superposition of all components, the received signal, is severely distorted. The dependence of delay on wavelength is known as *chromatic dispersion*, and we discuss it in more detail in the next section.

It therefore is important to distinguish between two types of *fiber bandwidths*: the *bandwidth for the optical carrier*, which is very wide (>10 THz), and the *bandwidth for the modulation signal*, which is limited by dispersion and is much, much smaller. For example, the modulation-signal bandwidth for 1 km of standard single-mode fiber is just a few 10 GHz, given a 1.55- $\mu$ m source with a 1-nm linewidth. We discuss this bandwidth and its dependence on linewidth further in Section 2.4. For 1 km of graded-index multimode fiber, the modulation-signal bandwidth is only 300 MHz to 3 GHz, and for a step-index multimode fiber, it is even lower at 6 MHz to 50 MHz [168].

Does this mean that we cannot really use the huge bandwidth that the fiber offers? Yes we can, if we use multiple optical carriers at different wavelengths and modulate each one at a modest bit rate, then the transmission becomes much more resilient to the various forms of dispersion. For example, instead of one wavelength modulated at 4 Tb/s, we could use 400 wavelengths, each one modulated at 10 Gb/s. This approach is known as *dense wavelength division multiplexing* (DWDM).

#### 2.2 **DISPERSION**

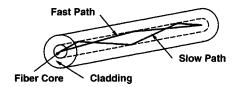

*Modal Dispersion.* An optical fiber consists of a core surrounded by a cladding that has a slightly lower refractive index than the core such that the light beam is guided by total internal reflection, as shown in Fig. 2.2. In principle, air, which has a lower refractive index than glass, could act as the cladding. However, the fiber surface then would be extremely sensitive to dirt and scratches, and two fibers touching each other would leak light. The invention of the *clad fiber* was a major breakthrough on the way to a practical optical fiber [43].

Fig. 2.2 Modal dispersion in a multimode fiber.

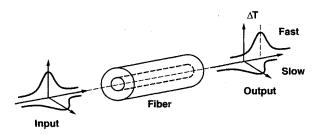

Depending on the size of the fiber core, there is only a single or several pathways (so-called modes) for the light beam to propagate through the fiber. The core of a *multimode fiber* (MMF) is large enough (50–100  $\mu$ m) for the light to take multiple pathways from the transmitter to the receiver, as shown in Fig. 2.2 (typically, several hundred modes exist). Each path has a slightly different propagation delay, thus producing a distorted (spread out) pulse at the receiver end. This effect is known as *modal dispersion*. The time difference between the longest and shortest path  $\Delta T$  for a so-called *graded-index multimode fiber* (GRIN-MMF) can be approximated by [5]

$$\Delta T = \frac{(n_{\rm cor} - n_{\rm clad})^2}{8c \cdot n_{\rm cor}} \cdot L, \qquad (2.1)$$

where L is the fiber length, c is the speed of light in vacuum, and  $n_{cor}$  and  $n_{clad}$ are the refractive indices of the core and cladding, respectively. With the typical values  $n_{cor} = 1.48$  and  $n_{cor} - n_{clad} = 0.02$  and a fiber length of 1 km, we find a propagation-delay variation of about 113 ps. Thus, modal dispersion is significant even for short fiber links. For example, at 10 Gb/s, the fiber length is limited to about 100 to 300 m. The core of a *single-mode fiber* (SMF) is much smaller (8–10  $\mu$ m) and permits only one pathway (a single mode) of light propagation from the transmitter to the receiver, and thus distortions due to modal dispersion are suppressed.<sup>2</sup> Note that the word 'mode' in SMF, MMF, and modal dispersion refers to *pathway* modes only. We see later that the single pathway mode in an SMF can be decomposed into two *polarization* modes, both of which propagate through the fiber and may cause polarization-mode dispersion.

SMF is preferred in telecommunication applications where distance matters (ultralong-haul, long-haul, metro, and access networks). MMF is mostly used within buildings for data communication (computer interconnects) and in consumer electronics. Its reach can be extended somewhat by the use of an adaptive equalizer in the receiver (cf. Section 4.7). Because the MMF has a larger core size, alignment of the fiber with another fiber or a laser chip is less critical. A transverse alignment error between a laser and an SMF of just 0.5  $\mu$ m causes a power penalty of about 1 dB, whereas the laser-to-MMF alignment is about 5× less critical [174]. Thus, components interfacing to MMF generally are lower in cost.

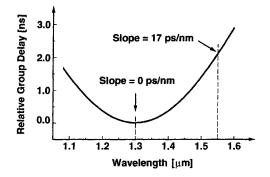

Chromatic Dispersion. Chromatic dispersion, also called group-velocity dispersion (GVD), is another source of signal distortions and is caused by different wavelengths (colors) traveling at different speeds through the fiber. Figure 2.3 illustrates how the group delay varies with wavelength for 1 km of standard SMF. We recognize that the change in group delay is large around  $1.55 \,\mu$ m, whereas it is nearly zero at  $1.3 \,\mu$ m. In practice, chromatic dispersion is specified by the *change* in group delay per nm wavelength and km length:

$$D = \frac{1}{L} \cdot \frac{\partial \tau}{\partial \lambda},\tag{2.2}$$

where D is known as the *dispersion parameter*, L is the fiber length,  $\tau$  is the group delay, and  $\lambda$  is the wavelength. A standard SMF operated at 1.55  $\mu$ m has  $D = 17 \text{ ps/(nm \cdot km)}$ , which means that a change in wavelength of 1 nm will change the group delay by 17 ps in a 1-km piece of fiber (cf. Fig. 2.3). The dependence of D on wavelength is plotted together with the fiber loss in Fig. 2.1. [ $\rightarrow$  Problem 2.2]

How much pulse distortion is caused by chromatic dispersion depends on the spectral linewidth of the transmitter. If the transmitter operates at precisely a single wavelength, which implies an ideal, zero-linewidth laser without modulation, chromatic dispersion doesn't matter. However, if the transmitter operates over a range of wavelengths, as it does when transmitting information using a real laser, chromatic dispersion causes pulse distortions. The propagation time difference between the slowest and fastest wavelength for a transmitter that emits light over the range  $\Delta \lambda$

<sup>&</sup>lt;sup>2</sup>The reader may wonder why a 8- to 10- $\mu$ m core is small enough to ensure single-mode propagation of light with a wavelength of 1.3 to 1.55  $\mu$ m. It turns out that the condition for single-mode propagation is that the core diameter must be  $d < \lambda \cdot 0.766/\sqrt{n_{cor}^2 - n_{clad}^2}$  [5]. Because the difference between  $n_{cor}$  and  $n_{clad}$  is small (less than 1% for an SMF), the core can be made quite a bit larger than the wavelength  $\lambda$ , simplifying the light coupling into the fiber. Another advantage of the clad fiber!

Fig. 2.3 Relative group delay as a function of wavelength for 1 km of standard SMF.

can be derived from Eq. (2.2) as

$$\Delta T = |D| \cdot \Delta \lambda \cdot L. \tag{2.3}$$

The effects of chromatic dispersion on pulse spreading are rather important when designing a transmission system, and we discuss them in more detail in Section 2.4.

What can we do to reduce the chromatic dispersion  $|D| \cdot L$ ? Because dispersion is a linear phenomenon, it can be reversed by applying an equal amount of *negative* dispersion. This method is known as dispersion compensation, and so-called dispersion compensating fiber (DCF) with a large negative value of D such as  $-100 \text{ ps/(nm \cdot km)}$ is available for this purpose. For example, to compensate for the positive dispersion of 100 km of standard SMF, we can append 17 km of DCF, resulting in an overall dispersion of zero:  $100 \text{ km} \cdot 17 \text{ ps/(nm} \cdot \text{km}) + 17 \text{ km} \cdot (-100 \text{ ps/(nm} \cdot \text{km})) = 0.3$ Note that in such a system, at first each bit spreads out over many adjacent bit slots, resulting in a total mess, but then the DCF pulls all the bits back together again, producing a crisp optical signal. Alternatively, we can transmit at the  $1.3-\mu$ m wavelength, where the dispersion parameter D of a standard SMF is much smaller than at 1.55  $\mu$ m (see Fig. 2.1). But, as we know, at the 1.3- $\mu$ m wavelength the fiber loss is higher. To resolve this dilemma, fiber manufacturers have come up with the socalled dispersion-shifted fiber (DSF), which has a value of D close to zero at the  $1.55-\mu m$  wavelength while preserving the low loss of an SMF. This fiber, however, has a disadvantage in DWDM systems that we discuss in Section 2.3 on nonlinearities. The effects of chromatic dispersion also can be mitigated in the electrical domain by using a receiver with an equalizer (cf. Section 4.7). Because the optical phase information becomes lost in the detection process, this method is less capable than optical dispersion compensation; however, it may have a cost advantage.

<sup>&</sup>lt;sup>3</sup>Typically, perfect dispersion compensation can be achieved only at a single wavelength. In a DWDM system, the middle channel can be compensated perfectly, whereas the outer channels retain some residual dispersion.

**Polarization-Mode Dispersion.** Another source of distortions is *polarization-mode dispersion* (PMD), which is caused by different polarization modes traveling at different speeds. This effect occurs in fibers with a slightly elliptic core or asymmetrical mechanical stress. Figure 2.4 illustrates how, in such a fiber, horizontally and vertically polarized light propagates at slightly different speeds. The difference in arrival time,  $\Delta T$ , is known as *differential group delay* (DGD). Because, in general, the transmitter is exciting both polarization modes (horizontal and vertical), the receiver sees two time-shifted copies of the transmitted sequence superimposed on top of each other. The strength of each sequence depends on the alignment of the transmitter's linearly polarized light with the axes of the elliptic core.

Fig. 2.4 Polarization-mode dispersion in a short fiber segment.

In a long stretch of fiber, the situation is complicated by the fact that the fiber's effect on the polarization state (birefringence) changes randomly along its *length*. As a result, we have the following modifications. (i) The input polarization states that correspond to the fast and slow propagation are no longer linear states (i.e., horizontal and vertical) but general elliptic polarization states, which differ from fiber to fiber. These states are known as the input *principle states of polarization* (PSP). (ii) The differential group delay, averaged over many fibers, is proportional to the *square root* of the fiber length L (rather than the length itself) and can be written

$$\overline{\Delta T} = D_{PMD} \cdot \sqrt{L}, \qquad (2.4)$$

where  $D_{PMD}$  is the *polarization-mode dispersion parameter*. In addition to the statistical uncertainty, PMD also varies slowly over *time*, that is, the PSPs and  $D_{PMD}$  are a function of time. As a rule of thumb, we must keep  $\overline{\Delta T}$  below 10% of the bit interval (0.1/B) to keep the power penalty due to PMD almost permanently below 1 dB.<sup>4</sup> Another complication in real systems is the wavelength dependence of both the input PSPs and the DGD, which makes the PMD distortions look more complex than just a simple superposition of time-shifted copies of the transmitted signal (so-called *higher-order PMD* distortions).

<sup>&</sup>lt;sup>4</sup>More precisely, to ensure an outage probability of  $<10^{-7}$ , that is, <3 seconds/year during which the power penalty exceeds 1 dB we need  $\overline{\Delta T} < 0.1/B$  for RZ modulation and  $\overline{\Delta T} < 0.07/B$  for NRZ modulation [74].

What can we do against PMD? Recently manufactured fiber has a very low PMD parameter around  $D_{PMD} = 0.1 \text{ ps}/\sqrt{\text{km}}$ . This means that in a 100-km fiber, the average delay is only 1 ps; no problem, even for 40 Gb/s. Older fiber, which is widely deployed and has a slightly elliptic cross section of the fiber core as a result of manufacturing tolerances, has a much larger PMD parameter around  $D_{PMD} = 2 \text{ ps}/\sqrt{\text{km}}$ . In the latter case, we can use optical or electrical PMD mitigation techniques. In a simple optical PMD compensator, a fiber segment with strong intentional PMD, a so-called *polarization maintaining fiber* (PMF), is placed in front of the receiver to undo the PMD accumulated during transmission. In between the transmission fiber and the compensation fiber, a polarization controller must be inserted to make sure that the fast output PSP is fed into the slow input PSP of the compensation fiber and vice versa. Because the PMD is time varying, the polarization controller must be adjusted continuously with a feedback signal derived from the quality of the received signal. In a simple electrical PMD compensator, the distorted optical signal is converted first to an electrical signal with a photodetector (losing the polarization information). Then, an adaptive equalizer as part of the receiver removes as much distortion as possible (see Section 4.7). Again, because of the time-varying nature of PMD, it is necessary to adjust the equalizer characteristics continuously as a function of the received signal quality.

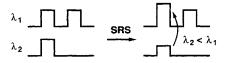

#### 2.3 NONLINEARITIES

Attenuation and dispersion are known as *linear* fiber effects because they can be described by a linear relationship between the fields of the lightwaves at the input and output of the fiber. Apart from these linear effects, the fiber suffers from a number of *nonlinear* effects that may distort and attenuate the optical signal or may produce crosstalk between optical channels. The most important of these effects are *self-phase modulation* (SPM), *cross-phase modulation* (CPM or XPM), *stimulated Raman scattering* (SRS), *stimulated Brillouin scattering* (SBS), and *four-wave mixing* (FWM). These effects become important in long optical links operated at high optical power levels. In single-wavelength systems, SPM, SRS, and SBS can cause pulse distortion and attenuation. In addition to that, in DWDM systems, CPM, SRS, SBS, and FWM can cause crosstalk between optical channels.

What can we do against these nonlinear effects? In general, nonlinear effects can be suppressed if the transmitted optical power is kept sufficiently low. One way to lower the transmit power without impacting the bit-error rate performance is to use forward error correction (cf. Section 4.11). As we have said, in a DWDM system, the bits in different channels may interact with each other through nonlinear effects, resulting in a change of pulse shape and amplitude (cf. Section 6.2.7). The longer the interacting bits stay together, the stronger the crosstalk distortions become. For this reason, it is advantageous if the different wavelength channels propagate at slightly different speeds, that is, if there is a small amount of chromatic dispersion. A special fiber, called *nonzero dispersion-shifted fiber* (NZ-DSF), has been developed that has a small value for |D| around 1 to 6 ps/(nm · km), large enough to create a "walk-off" between the bit streams, thus reducing nonlinear interactions, but small enough to limit the amount of dispersion compensation needed or to avoid it altogether.

#### 2.4 PULSE SPREADING DUE TO CHROMATIC DISPERSION

Modal dispersion can be suppressed with the use of SMF, and PMD is only of concern in long-haul and high-speed systems, but almost every optical transmission system is affected by chromatic dispersion. In the following, we investigate the pulse distortions caused by chromatic dispersion in greater detail.

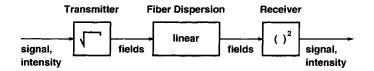

Nonlinear Character of Optical Fiber Communication. To transmit an optical signal over a fiber, we modulate the *intensity* of a light source, and to receive the signal, we detect the *intensity* of the light.<sup>5</sup> Let's assume that the fiber in between the transmitter and the receiver exhibits dispersion. We said earlier that dispersion is a linear phenomenon, but linear in the *fields* not the *intensity*! Thus, the complete communication channel can be modeled as shown in Fig. 2.5. The signal is converted to light with a proportional intensity; the light is carried by an electromagnetic field, which is proportional to the square-root of the intensity; the field disperses linearly in the fiber; the field at the end of the fiber is characterized by an intensity, which is proportional to it is generated. This is a *nonlinear* system! Note that the nonlinearity here is due to the square law relating the intensity and the field and has nothing to do with the nonlinearity in fibers discussed in the previous section.

Fig. 2.5 Communication channel with intensity modulation, fiber dispersion, and intensity detection.

Now we understand that, in general, we cannot apply linear system theory to analyze the pulse distortions caused by fiber dispersion, making this a rather nasty problem. (This same nonlinearity will bother us again when discussing optical and electrical dBs, and then again when we talk about optical noise.) However, there is an approximation that we can use under certain conditions. If we use a light source with a bandwidth much greater than the signal bandwidth, we can approximately describe the channel with a linear response [11]. With such a wide-linewidth source, the transmitter linewidth  $\Delta\lambda$  is approximately equal to the source linewidth  $\Delta\lambda_S$ ,

<sup>&</sup>lt;sup>5</sup>This method is known as *direct detection*. An alternative is *coherent detection*, but this subject is beyond the scope of this book.

and the effects of the modulating signal on  $\Delta\lambda$  can be neglected. In practice, this is the case for transmitters with a light-emitting diode (LED) or a Fabry-Perot (FP) laser source, as we see in Chapter 7. If we further assume that the source spectrum is Gaussian and we are operating at a wavelength far from zero dispersion, the impulse response of the channel turns out to be

$$h(t) = h(0) \cdot \exp\left(-\frac{t^2}{2 \cdot (\Delta T/2)^2}\right),$$

(2.5)

where

$$\Delta T = |D| \cdot \Delta \lambda \cdot L \tag{2.6}$$

and  $\Delta\lambda$  is the  $2\sigma$ -linewidth of the transmitter (or source). In other words, a Dirac impulse injected into one end of the fiber will spread out slowly into a Gaussian pulse as it propagates along the fiber. The  $2\sigma$ -width of the spreading pulse is the  $\Delta T$  given in Eq. (2.6). For example, a very narrow pulse launched into a standard SMF will spread out to 17 ps after 1 km given a 1.55- $\mu$ m source with a linewidth of 1 nm. Thus, the dispersion parameter D tells us how rapidly a narrow pulse is spreading out.

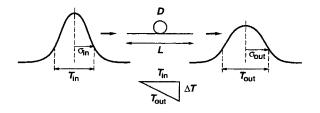

*Time-Domain Analysis.* Now that we have a linear model, we are on familiar territory and we can calculate how a regular (non-Dirac) data pulse spreads out. The math is easiest if we assume that the transmitted pulse is Gaussian. The convolution of the (Gaussian) input pulse with the (Gaussian) impulse response produces a Gaussian output pulse! We find the relationship between the  $2\sigma$ -width of the input pulse,  $T_{in}$ , and the  $2\sigma$ -width of the output pulse  $T_{out}$  to be

$$T_{\rm out} = \sqrt{T_{\rm in}^2 + \Delta T^2}.$$

(2.7)

This situation is illustrated in Fig. 2.6. Although in practice we are not likely to use Gaussian pulses, this simple calculation helps us to understand under which circumstances chromatic dispersion becomes important. For example, on 1 km of standard SMF with a source linewidth of 1 nm at 1.55  $\mu$ m, a 100-ps pulse will broaden to  $\sqrt{(100 \text{ ps})^2 + (17 \text{ ps})^2} = 101.4 \text{ ps.}$  [ $\rightarrow$  Problem 2.3]

Fig. 2.6 Pulse spreading due to chromatic dispersion.

The maximum amount of spreading,  $\Delta T$ , that normally can be tolerated in an NRZ-modulated system is equal to half a bit period [46]:<sup>6</sup>

$$\Delta T \le \frac{1}{2B}.\tag{2.8}$$

This amount of spreading increases the pulse width by  $\sqrt{1^2 + 0.5^2} = 1.12$  or about 12% and causes a power penalty of approximately 1 dB [46].

As we can see from Eqs. (2.6) and (2.8), the linewidth of the source is of critical importance in determining the amount of pulse spreading in a dispersive fiber and thus the maximum bit rate and distance over which we can transmit.

*Frequency-Domain Analysis.* Given the expression for the impulse response of a dispersive fiber, we can easily transform it into the frequency domain and discuss the corresponding channel bandwidth. Transforming the Gaussian impulse response in Eq. (2.5) yields the Gaussian frequency response

$$H(f) = H(0) \cdot \exp\left(-\frac{(2\pi f)^2 (\Delta T/2)^2}{2}\right).$$

(2.9)

The 3-dB bandwidth of this optical intensity response can be found by setting the equation equal to  $1/2 \cdot H(0)$  and solving for f. Together with Eq. (2.6), we find [5]<sup>7</sup>

$$BW_{3dB} = \frac{0.375}{\Delta T} = \frac{0.375}{|D| \cdot \Delta \lambda \cdot L}.$$

(2.10)

This is the modulation-signal bandwidth due to chromatic dispersion first introduced in Section 2.1. Its value decreases as the fiber length L, the linewidth  $\Delta\lambda$ , or the dispersion parameter D increases. For example, 1 km of standard SMF with a source linewidth of 1 nm at 1.55  $\mu$ m has a bandwidth of just 22 GHz. If we replace the SMF with an NZ-DSF that has a dispersion parameter of only  $D = 5 \text{ ps/(nm \cdot km)}$ , the bandwidth increases to 75 GHz. [ $\rightarrow$  Problem 2.4]

Finally, what is the interpretation of the spreading limit, Eq. (2.8), in the frequency domain? Inserting Eq. (2.8) into Eq. (2.10), we find

$$BW_{3dB} \ge 0.75 \cdot B. \tag{2.11}$$

This means the fiber bandwidth must be made larger than 3/4 of the bit rate to avoid excessive distortions. [ $\rightarrow$  Problem 2.5]

*Narrow-Linewidth Source*. What happens if we use a light source with a bandwidth much smaller than the signal bandwidth? In practice, this situation occurs for

<sup>&</sup>lt;sup>6</sup>Note that in terms of the mean-square impulse spread  $\sigma_T^2 = (\Delta T/2)^2$ , this limit is  $\sigma_T \le 1/(4B)$ .

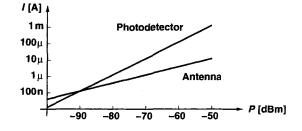

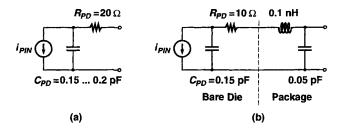

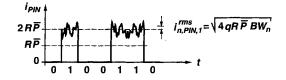

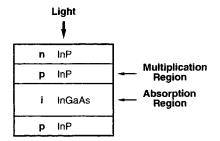

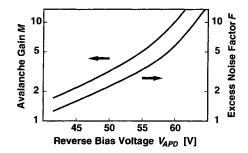

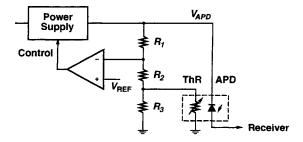

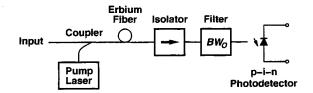

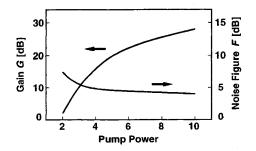

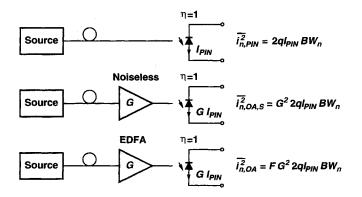

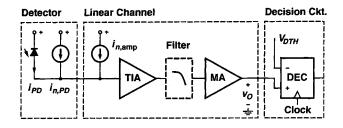

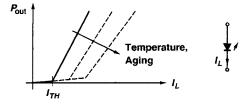

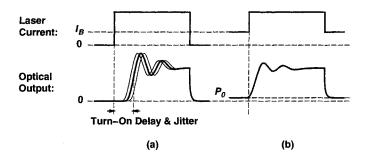

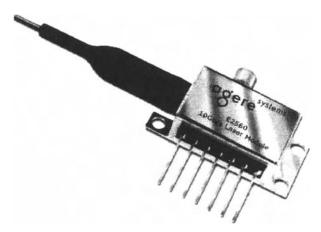

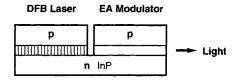

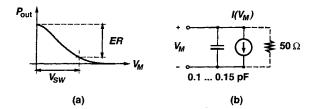

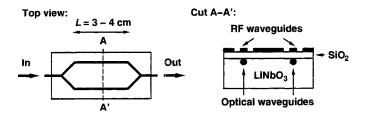

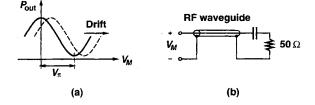

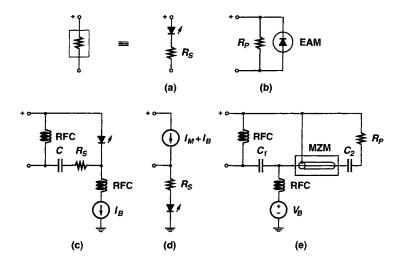

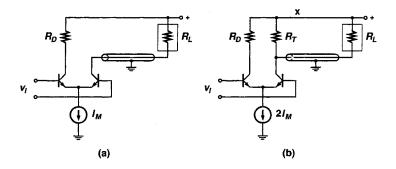

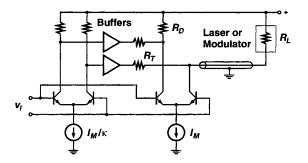

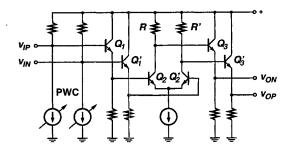

<sup>&</sup>lt;sup>7</sup>In the electrical domain, this bandwidth is the 6-dB bandwidth, because three optical dBs convert to six electrical dBs (cf. Section 3.1)!